Test coverage and Fault coverage are the two important quantities which measures how good the DFT logic was implemented on core design for controllability and observability of a design.

Test Coverage:

Test coverage is a measure of test quality of DFT, is the percentage of faults detected from among all testable faults. This is the number of most concern when you consider the testability of the design

Fault Coverage:

Fault Coverage consists of the percentage of faults detected from among all the faults that the test patterns generated by the tool

Where DT is detected faults class includes all the faults that the ATPG identifies as detected and this are classified into two groups

- Det_simulation (DS)

- Det_implication (DI)

PD – posdet or possible detected fault class includes all the faults that fault simulation identifies as possible detected but not hard to detect

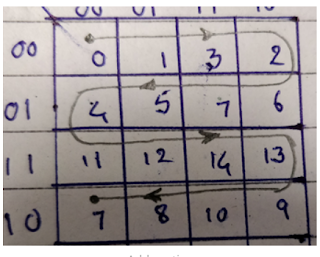

Let us see how the test coverage and fault coverage was calculated from snap shot of status report

From the report Total no of faults are given as 302778

Faults due to unused pins (UU), Tied pins (TI), Blocked Pins (BL), and redundant logic (RE) are untestable by tool and this faults must be excluded from the total number of faults while calculating the Test Coverage and considered while calculating the Fault Coverage.

UU+TI+BL+RE => 4984+1076+12+1072 = 7144

Thus Testable faults are given asTotal Faults – (UU+TI+BL+RE)

Total faults detected during simulation (DS) and implication (DI) are

DS +DI => 202752+75601+16 = 278369

In general posdet_credit will be set to zero and with this above faults numbers we can have Test Coverage and Fault Coverage

In this process TC and FC are calculated and we need to achieve 99 % Test Coverage for Stuck At fault model and 95% Test Coverage for At Speed fault model