Speed of the transistor is decided with Ion and Ioff. On current was increased as we go down the technology node because less Vt is required for small channel length and delay of the device is also reduced.When Device is off(i.e Vgs =0 and Vds=Vdd) there will be subthreshold current which contributes to the Ioff current and this current must be maintained low to reduce the static power. For better operation of the devices on current must be high and off current must be low.

- Ion current was increased with decrease in Vt ( this is reduced for every latest technology node)

- Ioff must be maintained low and this is achieved by reducing the subthreshold swing. Vt can be increased to reduce the Ioff but this will affect the Ion current of the device and delays of the devices will be affected.

Below image gives the equations of Ioff current and sub threshold swing

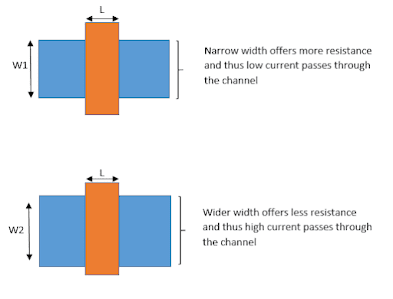

W represents the width of the channel

L represents the length of the channel

Vgs represents the gate to source voltage

Cox represents the oxide capacitance

Vt represents the threshold voltage of the devices.

From the above equations we can say Ioff can be reduced by changing S(subthershold swing) ,this can be achieved two ways

- By Increasing the Cox i.e. using thinner oxide

- By reducing Cdep of the device, this can be done by increasing Wdep.

Oxide capacitance can be increased by using the thinner oxide or high dielectric materials. Thickness of the oxide layers cannot be reduced beyond the 1nm , if it is beyond the 1nm , there will be a breakdown of the oxide material and tunnelling leakage current increases.

Because of the above limitation in thickness researchers started using the high K dielectric materials. Like 6nm thick HFO2 is equivalent to 1nm thick of Sio2 in the sense that both the films produce the same Cox. Like very solution as some negative effect, high K dielectrics are highly unstable and they react with the substrate.By inserting a thin Sio2 layer between substrate and dielectric material the chemical reaction can be reduced. High K dielectric materials offer lower surface mobility than Si/Sio2 which is a disadvantage .

Cdep can be reduced by increasing the Wdep, this can be done by decreasing the doping concentration because Wdep is inversely proportional to Nsub (doping concentration).

For a Device to work properly, we need to change Wdep, Tox, Xj(drain junction depth) proportional to change in channel length